# STM32 Cortex®-M0+ MCUs programming manual

## Introduction

This programming manual provides information for application and system-level software developers. It gives a full description of the programming model, instruction set, and core peripherals of the Cortex® M0+ processor.

Cortex®-M0+ is a high performance 32-bit processor designed for integration in microcontrollers. It offers significant benefits to developers, including:

- Outstanding processing performance combined with fast interrupt handling

- Enhanced system debug with extensive breakpoint options

- Efficient processor core, system, and memories

- Ultralow power consumption with integrated sleep modes

- · Platform security

Table 1. Applicable products

| Туре             | Products                                                        |  |

|------------------|-----------------------------------------------------------------|--|

| Microcontrollers | STM32C0 series, STM32G0 series, STM32L0 series, STM32WB series, |  |

|                  | STM32WL5x product line                                          |  |

# 1 About this document

This document provides the information required for application and system-level software development. It does not provide information on debug components, features, or operation.

This material is for microcontroller software and hardware engineers, including those who have no experience of Arm<sup>®</sup>.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

# 1.1 Typographical conventions

The typographical conventions used in this document are:

| italic           | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bold             | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.        |

| monospace        | Denotes text that the user can enter at the keyboard, such as commands, file and program names, and source code.                             |

| monospace        | Denotes a permitted abbreviation for a command or option. The user can enter the underlined text instead of the full command or option name. |

| monospace italic | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                |

| monospace bold   | Denotes language keywords when used outside example code.                                                                                    |

| < and >          | Enclose replaceable terms for assembler syntax where they appear in code or code fragments. For example:                                     |

|                  | LDRSB <cond> <rt>, [<rn>, #<offset>]</offset></rn></rt></cond>                                                                               |

# 1.2 List of abbreviations for registers

The following abbreviations are used in register descriptions:

| read/write (rw)     | The software can read and write to these bits.                                   |

|---------------------|----------------------------------------------------------------------------------|

| read-only (r)       | The software can only read these bits.                                           |

| write only (w)      | The software can only write to this bit.                                         |

| write-only (w)      | Reading the bit returns the reset value.                                         |

| road/act (ra)       | The software can read as well as set this bit.                                   |

| read/set (rs)       | Writing '0' has no effect on the bit value.                                      |

| read/clear (rc_w)   | The software can read as well as clear this bit by writing any value.            |

| read/clear (rc w1)  | The software can read as well as clear this bit by writing 1.                    |

| read/clear (rc_w r) | Writing '0' has no effect on the bit value.                                      |

| read/clear (rc w0)  | The software can read as well as clear this bit by writing 0.                    |

| read/clear (rc_wo)  | Writing '1' has no effect on the bit value.                                      |

| toggle (t)          | The software can only toggle this bit by writing '1'. Writing '0' has no effect. |

| Reserved (Res.)     | Reserved bit, must be kept at reset value.                                       |

|                     |                                                                                  |

# 1.3 About the Cortex® M0+ processor and core peripherals

The Cortex®-M0+ processor is an entry-level 32-bit Arm® Cortex® processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

A simple architecture that is easy to learn and program.

PM0223 - Rev 7 page 2/81

- Ultra-low power, energy-efficient operation.

- Excellent code density.

- Deterministic, high-performance interrupt handling.

- Upward compatibility with Cortex-M processor family.

- Platform security robustness, with optional integrated memory protection unit (MPU).

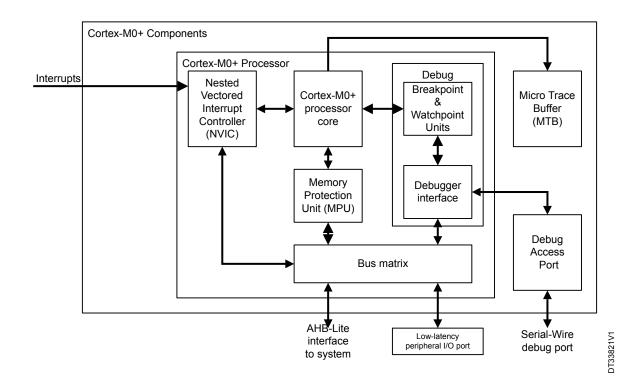

Figure 1. Cortex®-M0+ implementation

The Cortex®-M0+ processor is built on a 32-bit processor core that is highly optimized for area and power, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex®-M0+ processor implements the ARMv6-M architecture, which is based on the 16-bit Thumb® instruction set and includes Thumb-2 technology. This provides the exceptional performance expected of a modern 32-bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

The Cortex®-M0+ processor closely integrates a configurable nested vectored interrupt controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- Includes a non-maskable interrupt (NMI).

- Provides zero jitter interrupt option.

- Provides four interrupt priority levels.

The tight integration of the processor core and NVIC provides fast execution of interrupt service routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes that include a deep-sleep function that enables the entire device to be rapidly powered down.

PM0223 - Rev 7 page 3/81

## 1.3.1 System-level interface

The Cortex®-M0+ processor provides a single system-level interface using AMBA® technology to provide high speed low latency memory accesses.

The Cortex®-M0+ processor has an optional memory protection unit (MPU) that provides fine grain memory control, enabling applications to use multiple privilege levels, separating and protecting code, data, and stack on a task-by-task basis. Such requirements are becoming critical in many embedded applications such as automotive systems.

## 1.3.2 Integrated configurable debug

The Cortex®-M0+ processor implements a complete hardware debug solution, with extensive hardware breakpoint data, and watchpoint options. This provides high system visibility of the processor, memory, and peripherals through a <2-pin serial wire debug (SWD) port> that is ideal for microcontrollers and other small package devices.

## 1.3.3 Cortex<sup>®</sup>-M0+ processor feature summary

- Thumb instruction set with Thumb-2 technology.

- High code density with 32-bit performance.

- User and privileged mode execution.

- Tools and binary upwards compatible with Cortex<sup>®</sup>-M processor family.

- Integrated ultra low-power sleep modes.

- Efficient code execution enabling slower processor clock or increased sleep time.

- Single-cycle 32-bit hardware multiplier.

- Zero jitter interrupt handling.

- Memory protection unit (MPU) for safety-critical applications.

- Low latency, high-speed peripheral I/O port.

- A vector table offset register.

- · Extensive debug capabilities.

## 1.3.4 Cortex®-M0+ core peripherals

These are:

## **Nested vectored interrupt controller (NVIC)**

The NVIC is an embedded interrupt controller that supports low latency interrupt processing.

#### System control block

The System control block (SCB) is the programmers model interface to the processor. It provides system implementation information and system control, including configuration, control, and reporting of system exceptions.

## System timer

The system timer, SysTick, is a 24-bit count-down timer. Use this as a real time operating system (RTOS) tick timer or as a simple counter.

#### Memory protection unit

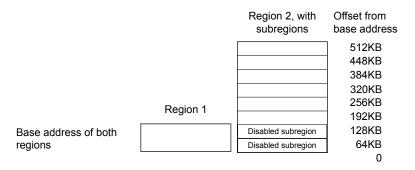

The memory protection unit (MPU) improves system reliability by defining the memory attributes for different memory regions. It provides up to eight different regions, and an optional predefined background region.

#### I/O port

The I/O port provides single-cycle loads and stores to tightly coupled peripherals.

PM0223 - Rev 7 page 4/81

# 2 Cortex®-M0+ processor

## 2.1 Programmers model

This section describes the Cortex®-M0+ programmers model. In addition to the individual core register descriptions, it contains information about the processor modes, privilege levels for software execution, and stacks.

#### 2.1.1 Processor modes and privilege levels for software execution

The processor modes are:

Handler mode Handles exceptions. The processor returns to thread mode when it has finished all exception processing.

The privilege levels for software execution are:

The software:

Unprivileged

- Has limited access to system registers using the MSR and MRS instructions, and cannot use the CPS instruction to mask interrupts.

- Cannot access the system timer, NVIC, or system control block.

- Might have restricted access to memory or peripherals.

Privileged

The software can use all the instructions and has access to all resources. Privileged software executes at the privileged level.

In thread mode, the CONTROL register controls whether software execution is privileged or unprivileged, see CONTROL register. In Handler mode, software execution is always privileged.

Only privileged software can write to the CONTROL register to change the privilege level for software execution in thread mode. Unprivileged software can use the SVC instruction to make a supervisor call to transfer control to privileged software.

## 2.1.2 Stacks

The processor uses a full descending stack. This means that the stack pointer indicates the last stacked item on the stack memory. When the processor pushes a new item onto the stack, it decrements the stack pointer and then writes the item to the new memory location. The processor implements two stacks, the main stack and the process stack, with independent copies of the stack pointer, see Stack pointer.

In thread mode, the CONTROL register controls whether the processor uses the main stack or the process stack, see CONTROL register. In handler mode, the processor always uses the main stack. The options for processor operations are:

Table 2. Summary of processor mode, execution privilege level, and stack use options

| Processor mode | Used to execute    | Privilege level for software execution    | Stack used                                 |

|----------------|--------------------|-------------------------------------------|--------------------------------------------|

| Thread         | Applications       | Privileged or unprivileged <sup>(1)</sup> | Main stack or process stack <sup>(1)</sup> |

| Handler        | Exception handlers | Always privileged                         | Main stack                                 |

1. See CONTROL register

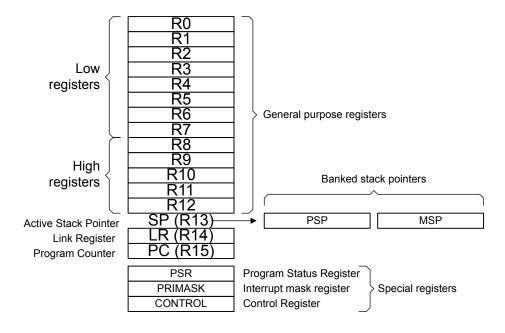

## 2.1.3 Core registers

The processor core registers are:

PM0223 - Rev 7 page 5/81

Figure 2. Processor core registers

Table 3. Core register set summary

| Name    | Type <sup>(1)</sup> | Reset value            | Description                         |

|---------|---------------------|------------------------|-------------------------------------|

| R0-R12  | RW                  | Unknown                | General purpose registers.          |

| MSP     | RW                  | See description        | Stack pointer.                      |

| PSP     | RW                  | Unknown                | Stack pointer                       |

| LR      | RW                  | Unknown                | Link register                       |

| PC      | RW                  | See description        | Program counter                     |

| PSR     | RW                  | Unknown <sup>(2)</sup> | Program status register             |

| APSR    | RW                  | Unknown                | Application program status register |

| IPSR    | RO                  | 0x00000000             | Interrupt program status register   |

| EPSR    | RO                  | Unknown                | Execution program status register   |

| PRIMASK | RW                  | 0x00000000             | Priority mask register              |

| CONTROL | RW                  | 0x00000000             | CONTROL register                    |

- 1. Describes access type during program execution in thread mode and handler mode. Debug access can differ.

- 2. Bit[24] is the T-bit and is loaded from bit[0] of the reset vector.

#### **General purpose registers**

R0-R12 are 32-bit general purpose registers for data operations.

## Stack pointer

The stack pointer (SP) is register R13. In thread mode, bit[1] of the CONTROL register indicates the stack pointer to use:

- 0 = Main Stack Pointer (MSP). This is the reset value.

- 1 = Process Stack Pointer (PSP).

133822V1

PM0223 - Rev 7 page 6/81

On reset, the processor loads the MSP with the value from address 0x00000000.

#### Link register

The link register (LR) is register R14. It stores the return information for subroutines, function calls, and exceptions. On reset, the LR value is unknown.

#### **Program counter**

The program counter (PC) is register R15. It contains the current program address. On reset, the processor loads the PC with the value of the reset vector, which is at address  $0 \times 00000004$ . Bit[0] of the value is loaded into the EPSR T-bit at reset and must be 1.

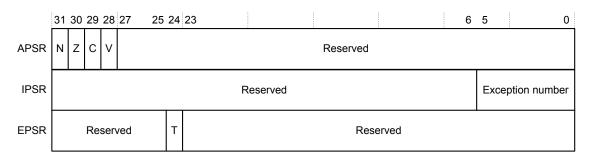

### Program status register

The program status register (PSR) combines:

- Application program status register (APSR).

- Interrupt program status register (IPSR).

- Execution program status register (EPSR).

These registers are allocated as mutually exclusive bitfields within the 32-bit PSR. The PSR bit assignments are:

Figure 3. APSR, IPSR, and EPSR bit assignments

Access these registers individually or as a combination of any two or all three registers, using the register name as an argument to the MSR or MRS instructions. For example:

- Read all of the registers using PSR with the MRS instruction.

- Write to the APSR using APSR with the MSR instruction.

The PSR combinations and attributes are:

Table 4. PSR register combinations

| Register | Туре                 | Combination           |

|----------|----------------------|-----------------------|

| PSR      | RW <sup>(1)(2)</sup> | APSR, EPSR, and IPSR. |

| IEPSR    | RO                   | EPSR and IPSR.        |

| IAPSR    | RW <sup>(2)</sup>    | APSR and IPSR.        |

| EAPSR    | RW <sup>(1)</sup>    | APSR and EPSR.        |

- 1. Reads of the EPSR bits return zero, and the processor ignores writes to these bits.

- 2. The processor ignores writes to the IPSR bits.

See the instruction descriptions Section 3.7.6 MRS and Section 3.7.7 MSR for more information about how to access the program status registers.

PM0223 - Rev 7 page 7/81

3823V1

## Application program status register

The APSR contains the current state of the condition flags, from previous instruction executions. See the register summary in Table 3. Core register set summary for its attributes. The bit assignments are:

Table 5. APSR bit assignment

| Bits   | Name | Description           |

|--------|------|-----------------------|

| [31]   | N    | Negative flag.        |

| [30]   | Z    | Zero flag.            |

| [29]   | С    | Carry or borrow flag. |

| [28]   | V    | Overflow flag.        |

| [27:0] | -    | Reserved.             |

See Section 3.3.6 Conditional execution for more information about the APSR negative, zero, carry or borrow, and overflow flags.

## Interrupt program status register

The IPSR contains the exception number of the current interrupt service routine (ISR). See the register summary in Table 3. Core register set summary for its attributes. The bit assignments are:

Table 6. IPSR bit assignments

| Bits   | Name             | Function                                                |

|--------|------------------|---------------------------------------------------------|

| [31:6] | -                | Reserved                                                |

|        |                  | This is the number of the current exception:            |

|        |                  | 0 = Thread mode.                                        |

|        |                  | 1 = Reserved.                                           |

|        |                  | 2 = NMI.                                                |

|        |                  | 3 = HardFault.                                          |

|        | Exception number | 4-10 = Reserved.                                        |

|        |                  | 11 = SVCall.                                            |

| I5:01  |                  | 12, 13 = Reserved.                                      |

| [5:0]  |                  | 14 = PendSV.                                            |

|        |                  | 15 = SysTick   Reserved.                                |

|        |                  | 16 = IRQ0.                                              |

|        |                  |                                                         |

|        |                  |                                                         |

|        |                  | 47 = IRQ31.                                             |

|        |                  | 48-63 = Reserved.                                       |

|        |                  | see Section 2.3.2 Exception types for more information. |

## **Execution program status register**

The EPSR contains the thumb state bit.

See the register summary in Table 3. Core register set summary for the EPSR attributes. The bit assignments are:

PM0223 - Rev 7 page 8/81

| Table 7. | <b>EPSR</b> | bit ass | ignments |

|----------|-------------|---------|----------|

|----------|-------------|---------|----------|

| Bits    | Name | Function         |

|---------|------|------------------|

| [31:25] | -    | Reserved.        |

| [24]    | Т    | Thumb state bit. |

| [23:0]  | -    | Reserved.        |

Attempts by application software to read the EPSR directly using the MRS instruction always return zero. Attempts to write the EPSR using the MRS instruction are ignored. Fault handlers can examine the EPSR value in the stacked PSR to determine the cause of the fault. See Section 2.3.6 Exception entry and return. The following can clear the T bit to 0:

- Instructions BLX, BX, and POP{PC}.

- Restoration from the stacked xPSR value on an exception return.

- Bit[0] of the vector value on an exception entry.

Attempting to execute instructions when the T bit is 0 results in a HardFault or lockup. See Section 2.4.1 Lockup for more information.

#### Interruptible-restartable instructions

The interruptible-restartable instructions are LDM and STM, PUSH, POP, and MULS. When an interrupt occurs during the execution of one of these instructions, the processor abandons execution of the instruction. After servicing the interrupt, the processor restarts execution of the instruction from the beginning.

### **Exception mask register**

The exception mask register disables the handling of exceptions by the processor. Disable exceptions where they might impact on timing critical tasks or code sequences requiring atomicity.

To disable or reenable exceptions, use the MSR and MRS instructions, or the CPS instruction, to change the value of PRIMASK. Section 3.7.7 MSR and Section 3.7.2 CPS for more information.

#### Priority mask register

The PRIMASK register prevents activation of all exceptions with configurable priority. See the register summary in Table 3. Core register set summary for its attributes. The bit assignments are:

Table 8. PRIMASK register bit assignments

| Bits   | Name | Function                                                                  |

|--------|------|---------------------------------------------------------------------------|

| [31:1] | -    | Reserved.                                                                 |

|        |      | Prioritizable interrupt mask:                                             |

| [0]    | PM   | 0 = No effect.                                                            |

|        |      | 1 = Prevents the activation of all exceptions with configurable priority. |

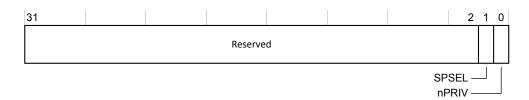

## **CONTROL** register

The CONTROL register controls the stack used, and the privilege level for software execution, when the processor is in thread mode. See the register summary in Table 3. Core register set summary for its attributes. The bit assignments are:

PM0223 - Rev 7 page 9/81

Figure 4. Control bit assignment

T33824//

Table 9. Control register bit assignments

| Bits   | Name  | Function                                                   |

|--------|-------|------------------------------------------------------------|

| [31:2] | -     | Reserved.                                                  |

|        |       | Defines the current stack:                                 |

| [4]    | SPSEL | 0 = MSP is the current stack pointer.                      |

| [1]    | SPSEL | 1 = PSP is the current stack pointer.                      |

|        |       | In Handler mode this bit reads as zero and ignores writes. |

|        |       | Defines the thread mode privilege level:                   |

| [0]    | nPRIV | 0 = Privileged.                                            |

|        |       | 1 = Unprivileged.                                          |

Handler mode always uses the MSP, so the processor ignores explicit writes to the active stack pointer bit of the CONTROL register when in Handler mode. The exception entry and return mechanisms automatically update the CONTROL register.

In an OS environment, it is recommended that threads running in thread mode use the process stack and the kernel and exception handlers use the main stack.

By default, thread mode uses the MSP. To switch the stack pointer used in thread mode to the PSP, use the MSR instruction to set the active stack pointer bit to 1, Section 3.7.6 MRS

Note:

When changing the stack pointer, software must use an ISB instruction immediately after the MSR instruction. This ensures that instructions after the ISB execute using the new stack pointer. See Section 3.7.5 ISB.

## 2.1.4 Exceptions and interrupts

The Cortex®-M0+ processor supports interrupts and system exceptions. The processor and the nested vectored interrupt controller (NVIC) prioritize and handle all exceptions. An interrupt or exception changes the normal flow of software control. The processor uses handler mode to handle all exceptions except for reset. See Exception entry and Exception return for more information.

The NVIC registers control interrupt handling. See Section 4.2 Nested vectored interrupt controller for more information.

#### 2.1.5 Data types

The processor:

- Supports the following data types:

- 32-bit words.

- 16-bit halfwords.

- 8-bit bytes.

- Manages all data memory accesses as little-endian or big-endian. Instruction memory and private peripheral bus (PPB) accesses are always little-endian. See Section 2.2.1 Memory regions, types, and attributes for more information.

PM0223 - Rev 7 page 10/81

## 2.1.6 Cortex® microcontroller software interface standard

Arm<sup>®</sup> provides the Cortex<sup>®</sup> microcontroller software interface standard (CMSIS) for programming Cortex<sup>®</sup>-M0+ microcontrollers. The CMSIS is an integrated part of the device driver library. For a Cortex<sup>®</sup>-M0+ microcontroller system, CMSIS defines:

- A common way to:

- Access peripheral registers.

- Define exception vectors.

- The names of:

- The registers of the core peripherals.

- The core exception vectors.

- A device-independent interface for RTOS kernels.

The CMSIS includes address definitions and data structures for the core peripherals in the Cortex®-M0+ processor. It also includes optional interfaces for middleware components comprising a TCP/IP stack and a flash file system.

The CMSIS simplifies software development by enabling the reuse of template code, and the combination of CMSIS-compliant software components from various middleware vendors. Software vendors can expand the CMSIS to include their peripheral definitions and access functions for those peripherals.

This document includes the register names defined by the CMSIS, and gives short descriptions of the CMSIS functions that address the processor core and the core peripherals.

Note:

This document uses the register short names defined by the CMSIS. In a few cases, these differ from the architectural short names that might be used in other documents.

The following sections give more information about the CMSIS:

- Section 2.5.4 Power management programming hints

- Section 3.2 Intrinsic functions

- Section 4.2.1 Accessing the Cortex®-M0+ NVIC registers using CMSIS

- Section 4.2.8 NVIC usage hints and tips

## 2.2 Memory model

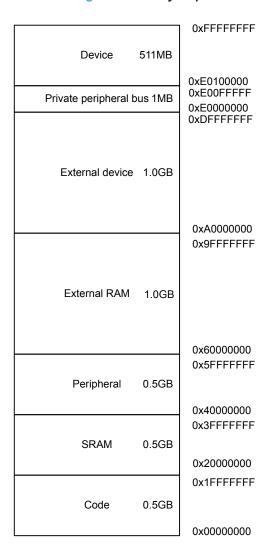

This section describes the processor memory map and the behavior of memory accesses. The processor has a fixed memory map that provides up to 4GB of addressable memory. The memory map is:

PM0223 - Rev 7 page 11/81

Figure 5. Memory map

The processor reserves regions of the private peripheral bus (PPB) address range for core peripheral registers, see Section 1.3 About the Cortex® M0+ processor and core peripherals.

## 2.2.1 Memory regions, types, and attributes

The memory map and the programming of the MPU splits into regions. Each region has a defined memory type, and some regions have additional memory attributes. The memory type and attributes determine the behavior of accesses to the region.

The memory types are:

Normal The processor can re-order transactions for efficiency, or perform speculative reads.

Device The processor preserves transaction order relative to other transactions to Device or Strongly-ordered

memory.

Strongly-ordered The processor preserves transaction order relative to all other transactions.

The different ordering requirements for device and Strongly ordered memory mean that the memory system can buffer a write to device memory, but must not buffer a write to Strongly ordered memory.

The additional memory attributes include.

JT33825V1

For a shareable memory region, the memory system provides data synchronization between bus masters in a system with multiple bus masters, for example, a processor with a DMA controller.

Strongly-ordered memory is always shareable.

Shareable

If multiple bus masters can access a non-shareable memory region, software must ensure data coherency between the bus masters.

<This description is required only if the device is likely to be used in systems where memory is shared between multiple processors.>

Execute Never (XN) Means the processor prevents instruction accesses. A HardFault exception is generated on executing an instruction fetched from an XN region of memory.

## 2.2.2 Memory system ordering of memory accesses

For most memory accesses caused by explicit memory access instructions, the memory system does not guarantee that the order in which the accesses complete matches the program order of the instructions, provided that any reordering does not affect the behavior of the instruction sequence. Normally, if correct program execution depends on two memory accesses completing in program order, software must insert a memory barrier instruction between the memory access instructions, see Section 2.2.2 Memory system ordering of memory accesses.

However, the memory system does guarantee some ordering of accesses to device and strongly ordered memory. For two memory access instructions A1 and A2, if A1 occurs before A2 in program order, the ordering of the memory accesses caused by the two instructions is:

Strongly-Device access Normal Α2 ordered Nonaccess A1 Shareable access shareable \_ Normal access \_ Device access, non-shareable < < Device access, shareable \_ < < Strongly-ordered access < < <

Figure 6. Ordering of memory accesses

- means that the memory system does not guarantee the ordering of the accesses.

- < means that accesses are observed in program order, that is A1 is always observed before A2.</li>

## 2.2.3 Behavior of memory accesses

The behavior of accesses to each region in the memory map is:

Table 10. Memory access behavior

| Address range            | Memory region | Memory type | XN | Description                                                          |

|--------------------------|---------------|-------------|----|----------------------------------------------------------------------|

| 0x00000000-<br>0x1FFFFFF | Code          | Normal      | -  | Executable region for program code. The user can also put data here. |

| 0x20000000-<br>0x3FFFFFF | SRAM          | Normal      | -  | Executable region for data. The user can also put code here.         |

| 0x4000000-<br>0x5FFFFFF  | Peripheral    | Device      | XN | External device memory.                                              |

| 0x60000000-<br>0x9FFFFFF | External RAM  | Normal      | -  | Executable region for data.                                          |

TO

page 13/81

PM0223 - Rev 7

| Address range             | Memory region             | Memory type          | XN | Description                                                                                                            |

|---------------------------|---------------------------|----------------------|----|------------------------------------------------------------------------------------------------------------------------|

| 0xA000000-<br>0xDFFFFFF   | External device           | Device               | XN | External device memory.                                                                                                |

| 0xE0000000-<br>0xE00FFFFF | Private Peripheral<br>Bus | Strongly-<br>ordered | XN | This region includes the NVIC, System timer, and System Control Block.  Only word accesses can be used in this region. |

For further information, see Section 2.2.1 Memory regions, types, and attributes

The code, SRAM, and external RAM regions can hold programs.

The MPU can override the default memory access behavior described in this section. For more information, see Section 4.5 Memory protection unit.

## 2.2.4 Additional memory access constraints for caches and shared memory

When a system includes caches or shared memory, some memory regions have additional access constraints, and some regions are subdivided, as Table 11. Memory region shareability and cache policies shows:

Address range **Memory region Memory type** Shareability Cache policy 0x0000000 - 0x1FFFFFF WT Code Normal 0x20000000 - 0x3FFFFFFF SRAM Normal **WBWA** 0x4000000- 0x5FFFFFF Peripheral Device 0x60000000 - 0x7FFFFFFF **WBWA** External RAM Normal 0x80000000 - 0x9FFFFFFF WT 0xA000000- 0xBFFFFFF Shareable External device Device 0xC000000- 0xDFFFFFF Non-shareable 0×E0000000- 0xE00FFFFF Private Peripheral Bus Strongly- ordered Shareable 0xE0100000- 0xFFFFFFF Device Device

Table 11. Memory region shareability and cache policies

#### Note:

For further information on memory types and shareability, see Section 2.2.1 Memory regions, types, and attributes.

Cache policy: T = Write through, no write allocate. WBWA = Write back, write allocate.

## 2.2.5 Software ordering of memory accesses

The order of instructions in the program flow does not always guarantee the order of the corresponding memory transactions. This is because:

- The processor can reorder some memory accesses to improve efficiency, providing this does not affect the behavior of the instruction sequence.

- Memory or devices in the memory map might have different wait states.

- Some memory accesses are buffered or speculative.

Section 2.2.2 Memory system ordering of memory accesses describes the cases where the memory system guarantees the order of memory accesses. Otherwise, if the order of memory accesses is critical, software must include memory barrier instructions to force that ordering. The processor provides the following memory barrier instructions:

DMB The Data Memory Barrier (DMB) instruction ensures that outstanding memory transactions complete before subsequent memory transactions. See Section 3.7.3 DMB.

DSB The Data Synchronization Barrier (DSB) instruction ensures that outstanding memory transactions complete before subsequent instructions execute. See Section 3.7.4 DSB.

PM0223 - Rev 7 page 14/81

ISB The Instruction Synchronization Barrier (ISB) ensures that the effect of all completed memory transactions is recognizable by subsequent instructions. See Section 3.7.5 ISB.

The following are examples of using memory barrier instructions:

| Vector table         | If the program changes an entry in the vector table, and then enables the corresponding exception, use a DMB instruction between the operations. This ensures that if the exception is taken immediately after being enabled the processor uses the new exception vector. |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Self-modifying code  | If a program contains self-modifying code, use an ISB instruction immediately after the code modification in the program. This ensures subsequent instruction execution uses the updated program.                                                                         |

| Memory map switching | If the system contains a memory map switching mechanism, use a DSB instruction after switching the memory map. This ensures subsequent instruction execution uses the updated memory map                                                                                  |

| MPU programming      | Use a DSB followed by an ISB instruction or exception return to ensure that the new MPU configuration is used by subsequent instructions.                                                                                                                                 |

| VTOR programming     | If the program updates the value of the VTOR, use a DMB instruction to ensure that the new vector table is used for subsequent exceptions.                                                                                                                                |

Memory accesses to strongly ordered memory, such as the system control block, do not require the use of DMB instructions.

## 2.2.6 Memory endianness

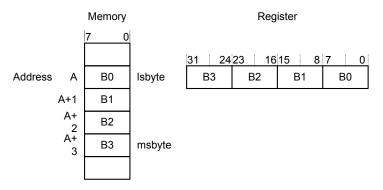

The processor views memory as a linear collection of bytes numbered in ascending order from zero. For example, bytes 0-3 hold the first stored word, and bytes 4-7 hold the second stored word. Little-endian format describes how words of data are stored in memory.

#### Little-endian format

In little-endian format, the processor stores the least significant byte (Isbyte) of a word at the lowest-numbered byte, and the most significant byte (msbyte) at the highest-numbered byte. For example:

Figure 7. Little-endian format example

DT33827V1

# 2.3 Exception model

This section describes the exception model.

## 2.3.1 Exception states

Each exception is in one of the following states:

Inactive The exception is not active and not pending.

Pending The exception is waiting to be serviced by the processor.

PM0223 - Rev 7

An interrupt request from a peripheral or from software can change the state of the corresponding interrupt to pending.

An exception that is being serviced by the processor but has not completed.

Active An exception handler can interrupt the execution of another exception handler. In this case both exceptions

are in the active state.

Active and pending

The exception is being serviced by the processor and there is a pending exception from the same source.

## 2.3.2 Exception types

NMI

**SVCall**

PendSV

SysTick

Interrupt

(IRQ)

The exception types are:

Reset is invoked on power-up or a warm reset. The exception model treats reset as a special form of exception.

When reset is asserted, the operation of the processor stops, potentially at any point in an instruction. When reset is deasserted, execution restarts from the address provided by the reset entry in the vector table.

Execution restarts as privileged execution in thread mode.

A Non-Maskable Interrupt (NMI) can be signaled by a peripheral or triggered by software. This is the highest priority exception other than reset. It is permanently enabled and has a fixed priority of -2. NMIs cannot be:

Masked or prevented from activation by any other exception.

Preempted by any exception other than Reset.

HardFault A HardFault is an exception that occurs because of an error during normal or exception processing. HardFaults have a fixed priority of -1, meaning they have higher priority than any exception with configurable priority.

A Supervisor Call (SVC) is an exception that is triggered by the SVC instruction. In an OS environment, applications can use SVC instructions to access OS kernel functions and device drivers.

PendSV is an interrupt-driven request for system-level service. In an OS environment, use PendSV for context switching when no other exception is active.

A SysTick exception is an exception that the system timer generates when it reaches zero. Software can also generate a SysTick exception. In an OS environment, the processor can use this exception as system tick.

An interrupt, or IRQ, is an exception signaled by a peripheral, or generated by a software request. All interrupts are asynchronous to instruction execution. In the system, peripherals use interrupts to communicate with the processor.

Table 12. Properties of the different exception types

| Exception<br>number <sup>(1)</sup> | IRQ<br>number <sup>(1)</sup> | Exception type  | Priority                                                            | Vector address <sup>(2)</sup>                   | Activation   |

|------------------------------------|------------------------------|-----------------|---------------------------------------------------------------------|-------------------------------------------------|--------------|

| 1                                  | -                            | Reset           | -3, the highest                                                     | 0x0000004                                       | Asynchronous |

| 2                                  | -14                          | NMI             | -2                                                                  | 0x00000008                                      | Asynchronous |

| 3                                  | -13                          | HardFault       | -1                                                                  | 0x000000C                                       | Synchronous  |

| 4-10                               | -                            | Reserved        | -                                                                   | _                                               | -            |

| 11                                 | -5                           | SVCall          | Configurable. See<br>Section 4.2.6 Interrupt priority<br>registers. | 0x0000002C                                      | Synchronous  |

| 12-13                              | -                            | Reserved        | -                                                                   | _                                               | -            |

| 14                                 | -2                           | PendSV          | Configurable. See<br>Section 4.2.6 Interrupt priority<br>registers  | 0x00000038                                      | Asynchronous |

| 15                                 | -1                           | SysTick         | Configurable. See<br>Section 4.2.6 Interrupt priority<br>registers  | 0x0000003C                                      | Asynchronous |

| 15                                 | -                            | Reserved        | -                                                                   | _                                               | -            |

| 16 and above                       | 0 and above                  | Interrupt (IRQ) | Configurable.<br>SeeSection 4.2.6 Interrupt priority<br>registers   | 0x00000040 and above. Increasing in steps of 4. | Asynchronous |

PM0223 - Rev 7 page 16/81

- 1. To simplify the software layer, the CMSIS only uses IRQ numbers. It uses negative values for exceptions other than interrupts. The IPSR returns the Exception number. See Interrupt program status register

- 2. See Figure 8. Vector table for more information.

For an asynchronous exception, other than reset, the processor can execute additional instructions between when the exception is triggered and when the processor enters the exception handler.

Privileged software can disable the exceptions that Table 12. Properties of the different exception types shows as having configurable priority, see Section 4.2.3 Interrupt clear-enable register.

For more information about HardFaults, see Section 2.4 Fault handling

## 2.3.3 Exception handlers

The processor handles exceptions using:

Interrupt Service Routines

(ISRs)

Interrupts IRQ0 to IRQ31 are the exceptions handled by ISRs

Fault handler HardFault is the only exception handled by the fault handler.

System handlers NMI, Pend

NMI, PendSV, SVCall SysTick, and HardFault are all system exceptions handled by system

handlers.

#### 2.3.4 Vector table

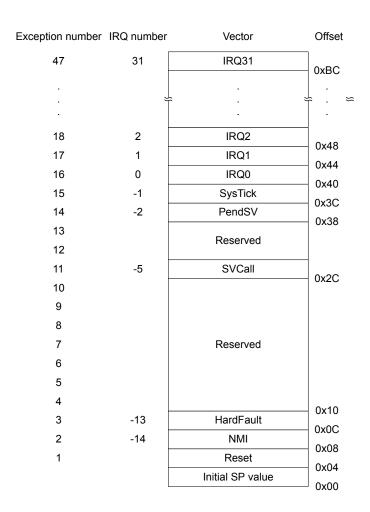

The vector table contains the reset value of the stack pointer, and the start addresses, also called exception vectors, for all exception handlers. Figure 8. Vector table shows the order of the exception vectors in the vector table. The least-significant bit of each vector must be 1, indicating that the exception handler is written in thumb code.

PM0223 - Rev 7 page 17/81

Figure 8. Vector table

JT33828V1

On system reset, the vector table is fixed at address 0x0000000. Privileged software can write to the VTOR to relocate the vector table start address to a different memory location with the respect to vector table size and granularity of TBLOFF settings (see Section 4.3.4 Vector table offset register).

# 2.3.5 Exception priorities

As Table 12. Properties of the different exception types shows, all exceptions have an associated priority, with:

- A lower priority value indicating a higher priority.

- Configurable priorities for all exceptions except reset, HardFault, and NMI.

If software does not configure any priorities, then all exceptions with a configurable priority have a priority of 0. For information about configuring exception priorities see:

- Section 4.3.8 System handler priority registers

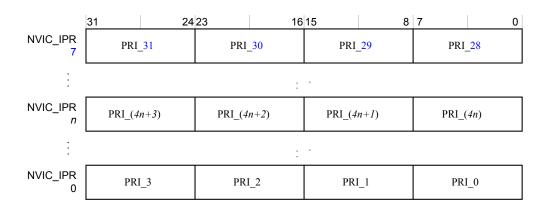

- Section 4.2.6 Interrupt priority registers

Note:

Configurable priority values are in the range 0-192, in steps of 64. The reset, HardFault, and NMI exceptions, with fixed negative priority values, always have higher priority than any other exception.

Assigning a higher priority value to IRQ[0] and a lower priority value to IRQ[1] means that IRQ[1] has higher priority than IRQ[0]. If both IRQ[1] and IRQ[0] are asserted, IRQ[1] is processed before IRQ[0].

PM0223 - Rev 7 page 18/81

If multiple pending exceptions have the same priority, the pending exception with the lowest exception number takes precedence. For example, if both IRQ[0] and IRQ[1] are pending and have the same priority, then IRQ[0] is processed before IRQ[1].

When the processor is executing an exception handler, the exception handler is preempted if a higher priority exception occurs. If an exception occurs with the same priority as the exception being handled, the handler is not preempted, irrespective of the exception number. However, the status of the new interrupt changes to pending.

## 2.3.6 Exception entry and return

Descriptions of exception handling use the following terms:

Preemption

When the processor is executing an exception handler, an exception can preempt the exception handler if its priority is higher than the priority of the exception being handled.

When one exception preempts another, the exceptions are called nested exceptions. See Exception entry for more information.

This occurs when the exception handler is completed, and:

There is no pending exception with sufficient priority to be serviced.

Return

The completed exception handler was not handling a late-arriving exception.

The processor pops the stack and restores the processor state to the state it had before the interrupt occurred. See Exception return for more information.

Tail-chaining

This mechanism speeds up exception servicing. On completion of an exception handler, if there is a pending exception that meets the requirements for exception entry, the stack pop is skipped and control transfers to the new exception handler.

Late-arriving except

This mechanism speeds up preemption. If a higher priority exception occurs during state saving for a previous exception, the processor switches to handle the higher priority exception and initiates the vector fetch for that exception. State saving is not affected by late arrival because the state saved would be the same for both exceptions. On return from the exception handler of the late-arriving exception, the normal tail-chaining rules

#### **Exception entry**

Exception entry occurs when there is a pending exception with sufficient priority and either:

- The processor is in thread mode.

- The new exception is of higher priority than the exception being handled, in which case the new exception preempts the exception being handled.

When one exception preempts another, the exceptions are nested.

Sufficient priority means that the exception has greater priority than any limit set by the mask register, see Exception mask register. An exception with less priority than this is pending but is not handled by the processor.

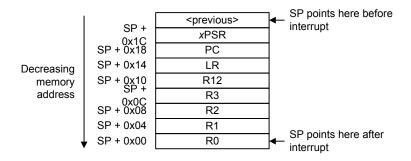

When the processor takes an exception, unless the exception is a tail-chained or a late-arriving exception, the processor pushes information onto the current stack. This operation is referred to as stacking and the structure of eight data words is referred to as a stack frame. The stack frame contains the following information:

Figure 9. Stack frame

JT33829V1

Immediately after stacking, the stack pointer indicates the lowest address in the stack frame. The stack frame is aligned to a double-word address.

The stack frame includes the return address. This is the address of the next instruction in the interrupted program. This value is restored to the PC at exception return so that the interrupted program resumes.

The processor performs a vector fetch that reads the exception handler start address from the vector table. When stacking is complete, the processor starts executing the exception handler. At the same time, the processor writes an EXC\_RETURN value to the LR. This indicates which stack pointer corresponds to the stack frame and what operation mode the processor was in before the entry occurred.

If no higher priority exception occurs during exception entry, the processor starts executing the exception handler, and automatically changes the status of the corresponding pending interrupt to active.

If another higher priority exception occurs during exception entry, the processor starts executing the exception handler for this exception, and does not change the pending status of the earlier exception. This is the late arrival case.

## **Exception return**

Exception return occurs when the processor is in handler mode and execution of one of the following instructions attempts to set the PC to an EXC\_RETURN value:

- A POP instruction that loads the PC.

- B PBX instruction using any register.

The processor saves an EXC\_RETURN value to the LR on exception entry. The exception mechanism relies on this value to detect when the processor has completed an exception handler. Bits[31:4] of an EXC\_RETURN value are 0xFFFFFFFFF. When the processor loads a value matching this pattern to the PC it detects that the operation is a not a normal branch operation and, instead that the exception is complete. As a result, it starts the exception return sequence. Bits[3:0] of the EXC\_RETURN value indicate the required return stack and processor mode, as Table 13. Exception return behavior shows.

| EXC_RETURN       | Description                                      |  |

|------------------|--------------------------------------------------|--|

|                  | Return to Handler mode.                          |  |

| 0xFFFFFFF1       | Exception return gets state from the main stack. |  |

|                  | Execution uses MSP after return.                 |  |

|                  | Return to thread mode.                           |  |

| 0xfffffff9       | Exception return gets state from MSP.            |  |

|                  | Execution uses MSP after return.                 |  |

|                  | Return to thread mode.                           |  |

| 0xfffffffD       | Exception return gets state from PSP.            |  |

|                  | Execution uses PSP after return.                 |  |

| All other values | Reserved.                                        |  |

Table 13. Exception return behavior

## 2.4 Fault handling

Faults are a subset of exceptions. See Section 2.3 Exception model. All faults result in the HardFault exception being taken or cause Lockup if they occur in the NMI or HardFault handler. The faults are:

- Execution of an SVC instruction at a priority equal or higher than SVCall.

- Execution of a BKPT instruction without a debugger attached.

- A system-generated bus error on a load or store.

- Execution of an instruction from an XN memory address.

- Execution of an instruction from a location for which the system generates a bus fault.

- A system-generated bus error on a vector fetch.

- Execution of an Undefined instruction.

- Execution of an instruction when not in Thumb state as a result of the T-bit being previously cleared to 0.

PM0223 - Rev 7 page 20/81

- An attempted load or store to an unaligned address.

- An MPU fault because of a privilege violation or an attempt to access an unmanaged region.

Note:

Only Reset and NMI can preempt the fixed priority HardFault handler. A HardFault can preempt any exception other than Reset, NMI, or another HardFault.

## **2.4.1** Lockup

The processor enters a Lockup state if a fault occurs when executing the NMI or HardFault handlers, or if the system generates a bus error when unstacking the PSR on an exception return using the MSP. When the processor is in lockup state, it does not execute any instructions. The processor remains in lockup state until one of the following occurs:

- It is reset.

- A debugger halts it.

- An NMI occurs and the current lockup is in the HardFault handler.

Note: If lockup state occurs in the NMI handler a subsequent NMI does not cause the processor to leave lockup state.

# 2.5 Power management

The Cortex®-M0+ processor sleep modes reduce power consumption:

- A sleep mode that stops the processor clock.

- A deep sleep mode that enters ultra low-power modes.

The SLEEPDEEP bit of the SCR selects which sleep mode is used, see Section 4.3.6 System control register (SCR). When entering the deep sleep mode, the PDSS bit in the PWR\_CR register selects entry in Stop or Standby mode. See the reference manual chapter "low-power modes" for details.

This section describes the mechanisms for entering sleep mode, and the conditions for waking up from sleep mode.

## 2.5.1 Entering sleep mode

This section describes the mechanisms software can use to put the processor into sleep mode.

The system can generate spurious wake-up events. For example, a debug operation wakes up the processor. For this reason, software must be able to put the processor back into sleep mode after such an event. A program might have an idle loop to put the processor back in to sleep mode.

## Wait for interrupt

The Wait For Interrupt instruction, WFI, causes immediate entry to sleep mode. When the processor executes a WFI instruction, it stops executing instructions and enters sleep mode. For further information, see Section 3.7.12 WFI.

#### Wait for event

The Wait For Event instruction, WFE, causes entry to sleep mode conditional on the value of a one-bit event register. When the processor executes a WFE instruction, it checks the value of the event register:

- 0 The processor stops executing instructions and enters sleep mode.

- 1 The processor sets the register to zero and continues executing instructions without entering sleep mode.

See Section 3.7.11 WFE for more information.

If the event register is 1, this indicates that the processor must not enter sleep mode on execution of a WFE instruction. Typically, this is because of the assertion of an external event, or because another processor in the system has executed a SEV instruction, see Section 3.7.9 SEV. Software cannot access this register directly.

#### Sleep-on-exit

If the SLEEPONEXIT bit of the SCR is set to 1, when the processor completes the execution of an exception handler and returns to thread mode it immediately enters sleep mode. Use this mechanism in applications that only require the processor to run when an interrupt occurs.

PM0223 - Rev 7 page 21/81

## 2.5.2 Wake-up from sleep mode

The conditions for the processor to wake up depend on the mechanism that caused it to enter sleep mode.

#### Wake-up from WFI or sleep-on-exit

Normally, the processor wakes up only when it detects an exception with sufficient priority to cause exception entry.

Some embedded systems might have to execute system restore tasks after the processor wakes up, and before it executes an interrupt handler. To achieve this set the PRIMASK.PM bit to 1. If an interrupt arrives that is enabled and has a higher priority than current exception priority, the processor wakes up but does not execute the interrupt handler until the processor sets PRIMASK.PM to zero. For more information about PRIMASK, see Exception mask register.

### Wake-up from WFE

The processor wakes up if:

- It detects an exception with sufficient priority to cause exception entry.

- It detects an external event signal. See Section 2.5.3 The external event input.

- In a multiprocessor system, another processor in the system executes a SEV instruction.

In addition, if the SEVONPEND bit in the SCR is set to 1, any new pending interrupt triggers an event and wakes up the processor, even if the interrupt is disabled or has insufficient priority to cause exception entry. For more information about the SCR. See Section 4.3.6 System control register (SCR).

#### 2.5.3 The external event input

The processor provides an external event input signal. This signal can be generated by peripherals. Tie this signal LOW if it is not used.

This signal can wake up the processor from WFE, or set the internal WFE event register to one to indicate that the processor must not enter sleep mode on a later WFE instruction, see Wait for event.

## 2.5.4 Power management programming hints

ISO/IEC C cannot directly generate the WFI, WFE, and SEV instructions. The CMSIS provides the following intrinsic functions for these instructions:

```

void __WFE(void) // Wait for Event

void __WFI(void) // Wait for Interrupt

void __SEV(void) // Send Event

```

PM0223 - Rev 7 page 22/81

# 3 Cortex®-M0+ instruction set

# 3.1 Instruction set summary

The processor implements a version of the thumb instruction set. Table 14. Cortex<sup>®</sup>-M0+ instructions lists the supported instructions.

In Table 14. Cortex®-M0+ instructions

- Angle brackets, <>, enclose alternative forms of the operand.

- Braces, {}, enclose optional operands and mnemonic parts.

- The operands column is not exhaustive.

For more information on the instructions and operands, see the instruction descriptions.

Table 14. Cortex®-M0+ instructions

| Mnemonic | Operands                      | Brief description                          | Flags   | Section                                      |

|----------|-------------------------------|--------------------------------------------|---------|----------------------------------------------|

| ADCS     | {Rd,} Rn, Rm                  | Add with carry                             | N,Z,C,V | Section 3.5.1 ADC, ADD, RSB, SBC, and SUB.   |

| ADD{S}   | {Rd,} Rn, <rm\#imm></rm\#imm> | Add                                        | N,Z,C,V | Section 3.5.1 ADC, ADD, RSB, SBC, and SUB.   |

| ADR      | Rd, label                     | PC-relative address to register            | -       | Section 3.4.1 ADR.                           |

| ANDS     | {Rd,} Rn, Rm                  | Bitwise AND                                | N,Z     | Section 3.5.2 AND, ORR, EOR, and BIC.        |

| ASRS     | {Rd,} Rm, <rs #imm></rs #imm> | Arithmetic shift right                     | N,Z,C   | Section 3.5.3 ASR, LSL, LSR, and ROR.        |

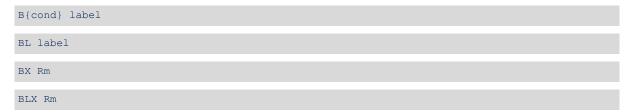

| B{cc}    | label                         | Branch {conditionally}                     | -       | Section 3.6.1 B, BL, BX, and BLX.            |

| BICS     | {Rd,} Rn, Rm                  | Bit clear                                  | N,Z     | Section 3.5.2 AND, ORR, EOR, and BIC.        |

| BKPT     | #imm                          | Breakpoint                                 | -       | Section 3.7.1 BKPT.                          |

| BL       | label                         | Branch with link                           | -       | Section 3.6.1 B, BL, BX, and BLX.            |

| BLX      | Rm                            | Branch indirect with link                  | -       | Section 3.6.1 B, BL, BX, and BLX.            |

| ВХ       | Rm                            | Branch indirect                            | -       | Section 3.6.1 B, BL, BX, and BLX.            |

| CMN      | Rn, Rm                        | Compare negative                           | N,Z,C,V | Section 3.5.4 CMP and CMN.                   |

| CMP      | Rn, <rm\#imm></rm\#imm>       | Compare                                    | N,Z,C,V | Section 3.5.4 CMP and CMN.                   |

| CPSID    | i                             | Change processor state, disable interrupts | -       | Section 3.7.2 CPS.                           |

| CPSIE    | i                             | Change processor state, enable interrupts  | -       | Section 3.7.2 CPS.                           |

| DMB      | -                             | Data memory barrier                        | -       | Section 3.7.3 DMB.                           |

| DSB      | -                             | Data synchronization barrier               | -       | Section 3.7.4 DSB.                           |

| EORS     | {Rd,} Rn, Rm                  | Exclusive OR                               | N,Z     | Section 3.5.2 AND, ORR, EOR, and BIC.        |

| ISB      | -                             | Instruction synchronization barrier        | -       | Section 3.7.5 ISB.                           |

| LDM      | Rn{!}, reglist                | Load multiple registers, increment after   | -       | Section 3.4.5 LDM and STM.                   |

| LDR      | Rt, label                     | Load register from PC-relative address     | -       | Section 3.4.2 LDR and STR, immediate offset. |

| LDR      | Rt, [Rn, <rm #imm>]</rm #imm> | Load register with word                    | -       | Section 3.4.2 LDR and STR, immediate offset. |

| LDRB     | Rt, [Rn, <rm #imm>]</rm #imm> | Load register with byte                    | -       | Section 3.4.2 LDR and STR, immediate offset. |

| LDRH     | Rt, [Rn, <rm #imm>]</rm #imm> | Load register with halfword                | -       | Section 3.4.2 LDR and STR, immediate offset. |

| LDRSB    | Rt, [Rn, <rm #imm>]</rm #imm> | Load register with signed byte             | -       | Section 3.4.2 LDR and STR, immediate offset. |

| LDRSH    | Rt, [Rn, <rm #imm>]</rm #imm> | Load register with signed halfword         | -       | Section 3.4.2 LDR and STR, immediate offset. |

| LSLS     | {Rd,} Rn, <rs #imm></rs #imm> | Logical shift left                         | N,Z,C   | Section 3.5.3 ASR, LSL, LSR, and ROR.        |

| LSRS     | {Rd,} Rn, <rs #imm></rs #imm> | Logical shift right                        | N,Z,C   | Section 3.5.3 ASR, LSL, LSR, and ROR.        |

| MOV{S}   | Rd, Rm                        | Move                                       | N,Z     | Section 3.5.5 MOV and MVN.                   |

PM0223 - Rev 7 page 23/81

| Mnemonic | Operands                      | Brief description                              | Flags   | Section                                      |

|----------|-------------------------------|------------------------------------------------|---------|----------------------------------------------|

| MRS      | Rd, spec_reg                  | Move to general register from special register | -       | Section 3.7.6 MRS.                           |

| MSR      | spec_reg, Rm                  | Move to special register from general register | N,Z,C,V | Section 3.7.7 MSR.                           |

| MULS     | Rd, Rn, Rm                    | Multiply, 32-bit result                        | N,Z     | Section 3.5.6 MULS.                          |

| MVNS     | Rd, Rm                        | Bitwise NOT                                    | N,Z     | Section 3.5.5 MOV and MVN.                   |

| NOP      | -                             | No operation                                   | -       | Section 3.7.8 NOP.                           |

| ORRS     | {Rd,} Rn, Rm                  | Logical OR                                     | N,Z     | Section 3.5.2 AND, ORR, EOR, and BIC.        |

| POP      | reglist                       | Pop registers from stack                       | -       | Section 3.4.6 PUSH and POP.                  |

| PUSH     | reglist                       | Push registers onto stack                      | -       | Section 3.4.6 PUSH and POP.                  |

| REV      | Rd, Rm                        | Byte-reverse word                              | -       | Section 3.5.7 REV, REV16, and REVSH.         |

| REV16    | Rd, Rm                        | Byte-reverse packed halfwords                  | -       | Section 3.5.7 REV, REV16, and REVSH.         |

| REVSH    | Rd, Rm                        | Byte-reverse signed halfword                   | -       | Section 3.5.7 REV, REV16, and REVSH.         |

| RORS     | {Rd,} Rn, Rs                  | Rotate right                                   | N,Z,C   | Section 3.5.3 ASR, LSL, LSR, and ROR.        |

| RSBS     | {Rd,} Rn, #0                  | Reverse subtract                               | N,Z,C,V | Section 3.5.1 ADC, ADD, RSB, SBC, and SUB.   |

| SBCS     | {Rd,} Rn, Rm                  | Subtract with carry                            | N,Z,C,V | Section 3.5.1 ADC, ADD, RSB, SBC, and SUB.   |

| SEV      | -                             | Send event                                     | -       | Section 3.7.9 SEV.                           |

| STM      | Rn!, reglist                  | Store multiple registers, increment after      | -       | Section 3.4.5 LDM and STM.                   |

| STR      | Rt, [Rn, <rm #imm>]</rm #imm> | Store register as word                         | -       | Section 3.4.2 LDR and STR, immediate offset. |

| STRB     | Rt, [Rn, <rm #imm>]</rm #imm> | Store register as byte                         | -       | Section 3.4.2 LDR and STR, immediate offset. |

| STRH     | Rt, [Rn, <rm #imm>]</rm #imm> | Store register as halfword                     | -       | Section 3.4.2 LDR and STR, immediate offset. |

| SUB{S}   | {Rd,} Rn, <rm\#imm></rm\#imm> | Subtract                                       | N,Z,C,V | Section 3.5.1 ADC, ADD, RSB, SBC, and SUB.   |

| SVC      | #imm                          | Supervisor call                                | -       | Section 3.7.10 SVC.                          |

| SXTB     | Rd, Rm                        | Sign extend byte                               | -       | Section 3.5.8 SXT and UXT.                   |

| SXTH     | Rd, Rm                        | Sign extend halfword                           | -       | Section 3.5.8 SXT and UXT.                   |

| TST      | Rn, Rm                        | Logical AND based test                         | N,Z     | Section 3.5.9 TST.                           |

| UXTB     | Rd, Rm                        | Zero extend a byte                             | -       | Section 3.5.8 SXT and UXT.                   |

| UXTH     | Rd, Rm                        | Zero extend a halfword                         | -       | Section 3.5.8 SXT and UXT.                   |

| WFE      | -                             | Wait for event                                 | -       | Section 3.7.11 WFE.                          |

| WFI      | -                             | Wait for interrupt                             | -       | Section 3.7.12 WFI.                          |

# 3.2 Intrinsic functions

ISO/IEC C code cannot directly access some Cortex $^{\$}$ -M0+ instructions. This section describes intrinsic functions that can generate these instructions, provided by the CMSIS and that might be provided by a C compiler. If a C compiler does not support an appropriate intrinsic function, the user might have to use the inline assembler to access the relevant instruction.

The CMSIS provides the following intrinsic functions to generate instructions that ISO/IEC C code cannot directly access:

Table 15. CMSIS intrinsic functions to generate some Cortex®-M0+ instructions

| Instruction | CMSIS intrinsic function         |  |

|-------------|----------------------------------|--|

| CPSIE i     | <pre>voidenable_irq(void)</pre>  |  |

| CPSID i     | <pre>voiddisable_irq(void)</pre> |  |

| ISB         | voidISB(void)                    |  |

PM0223 - Rev 7 page 24/81

| DSB   | voidDSB(void)                     |

|-------|-----------------------------------|

| DMB   | voidDMB(void)                     |

| NOP   | voidNOP(void)                     |

| REV   | uint32_tREV(uint32_t int value)   |

| REV16 | uint32_tREV16(uint32_t int value) |

| REVSH | uint32_tREVSH(uint32_t int value) |

| SEV   | voidSEV(void)                     |

| WFE   | voidWFE(void)                     |

| WFI   | voidWFI(void)                     |

The CMSIS also provides a number of functions for accessing the special registers using MRS and MSR instructions.

:

Table 16. CMSIS intrinsic functions to access the special registers

| Special register | Access | CMSIS function                                   |  |

|------------------|--------|--------------------------------------------------|--|

| PRIMASK          | Read   | uint32_tget_PRIMASK (void)                       |  |

| FRIMASK          | Write  | <pre>voidset_PRIMASK (uint32_t value)</pre>      |  |

| CONTROL          | Read   | uint32_tget_CONTROL (void)                       |  |

| CONTROL          | Write  | <pre>voidset_CONTROL (uint32_t value)</pre>      |  |

| MSP              | Read   | uint32_tget_MSP (void)                           |  |

| WSF              | Write  | <pre>voidset_MSP (uint32_t TopOfMainStack)</pre> |  |

| PSP              | Read   | uint32_tget_PSP (void)                           |  |

| FSF              | Write  | <pre>voidset_PSP (uint32_t TopOfProcStack)</pre> |  |

## 3.3 About the instruction descriptions

The following sections give more information about using the instructions:

- Section 3.3.1 Operands.

- Section 3.3.2 Restrictions when using PC or SP.

- Section 3.3.3 Shift operations.

- Section 3.3.4 Address alignment.

- Section 3.3.5 PCrelative expressions.

- Section 3.3.6 Conditional execution.

### 3.3.1 Operands

An instruction operand can be an Arm<sup>®</sup> register, a constant, or another instruction-specific parameter. Instructions act on the operands and often store the result in a destination register. When there is a destination register in the instruction, it is usually specified before the other operands.

## 3.3.2 Restrictions when using PC or SP

Many instructions are unable to use, or have restrictions on whether the user can use, the program counter (PC) or stack pointer (SP) for the operands or destination register. See instruction descriptions for more information.

Note:

When the user update the PC with a BX, BLX, or POP instruction, the bit[0] of any address must be 1 for correct execution. This is because this bit indicates the destination instruction set, and the Cortex-M0+ processor only supports thumb instructions. When a BL or BLX instruction writes the value of bit[0] into the LR it is automatically assigned the value 1.

PM0223 - Rev 7 page 25/81

## 3.3.3 Shift operations

Register shift operations move the bits in a register left or right by a specified number of bits, the shift length. Register shift can be performed directly by the instructions ASR, LSR, LSL, and ROR and the result is written to a destination register.

The permitted shift lengths depend on the shift type and the instruction, see the individual instruction description. If the shift length is 0, no shift occurs. Register shift operations update the carry flag except when the specified shift length is 0. The following subsections describe the various shift operations and how they affect the carry flag. In these descriptions, Rm is the register containing the value to be shifted, and n is the shift length.

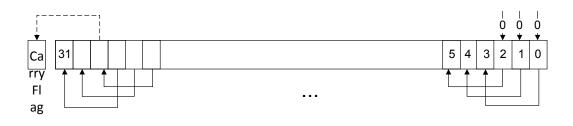

#### **ASR**

Arithmetic shift right by n bits moves the left-hand 32-n bits of the register Rm, to the right by n places, into the right-hand 32-n bits of the result, and it copies the original bit[31] of the register into the left-hand n bits of the result. See Figure 10. ASR#3.

The user can use the ASR operation to divide the signed value in the register Rm by  $2^n$ , with the result being rounded towards negative-infinity.

When the instruction is ASRS the carry flag is updated to the last bit shifted out, bit[n-1], of the register Rm

Note: If n is 32 or more, then all the bits in the result are cleared to 0.

If n is 33 or more and the carry flag is updated, it is updated to 0.

Figure 10. ASR#3

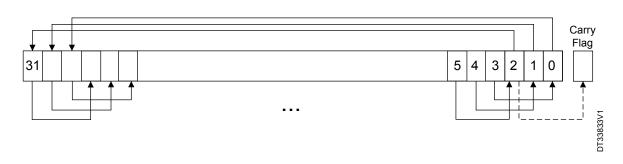

LSR

Logical shift right by n bits moves the left-hand 32-n bits of the register Rm, to the right by n places, into the right-hand 32-n bits of the result, and it sets the lefthand n bits of the result to 0. See Figure 11. LSR#3.

The user can use the LSR operation to divide the value in the register Rm by  $2^n$ , if the value is regarded as an unsigned integer.

When the instruction is LSRS, the carry flag is updated to the last bit shifted out, bit[n-1], of the register Rm

Note: If n is 32 or more, then all the bits in the result are cleared to 0.

If n is 33 or more and the carry flag is updated, it is updated to 0.

Figure 11. LSR#3

LSL

DT33830V1

DT33831

JT33832V1

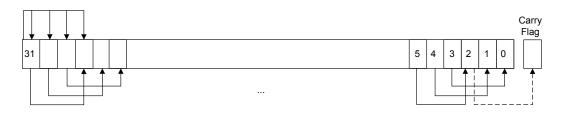

Logical shift left by n bits moves the right-hand 32-n bits of the register Rm, to the left by n places, into the left-hand 32-n bits of the result, and it sets the righthand n bits of the result to 0. See Section 3.3.3 Shift operations.

The user can use the LSL operation to multiply the value in the register Rm by  $2^n$ , if the value is regarded as an unsigned integer or a two's complement signed integer. Overflow can occur without warning.

When the instruction is LSLS the carry flag is updated to the last bit shifted out, bit[32-n],

of the register Rm. These instructions do not affect the carry flag when used with LSL#0.

Note: If n is 32 or more, then all the bits in the result are cleared to 0.

If n is 33 or more and the carry flag is updated, it is updated to 0.

Figure 12. LSL #3

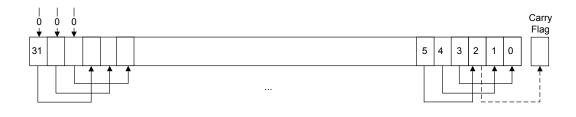

**ROR**

Rotate right by n bits moves the left-hand *32-n*bits of the register *Rm*, to the right by n places, into the right-hand *32-n* bits of the result, and it moves the righthand n bits of the register into the lefthand n bits of the result. See Figure 12. LSL #3.

When the instruction is RORS the carry flag is updated to the last bit rotation, bit[n-1], of the register Rm.

Note: If n is 32, then the value of the result is same as the value in Rm, and if the carry flag is updated, it is updated to bit[31] of Rm.

If ROR with shift length, n, greater than 32 is the same as ROR with shift length n-32.

Figure 13. ROR #3

## 3.3.4 Address alignment

An aligned access is an operation where a word-aligned address is used for a word, or multiple word access, or where a halfword-aligned address is used for a halfword access. Byte accesses are always aligned.

There is no support for unaligned accesses on the Cortex-M0+ processor. Any attempt to perform an unaligned memory access operation results in a HardFault exception.

PM0223 - Rev 7 page 27/81

## 3.3.5 PCrelative expressions

A PCrelative expression or label is a symbol that represents the address of an instruction or literal data. It is represented in the instruction as the PC value plus or minus a numeric offset. The assembler calculates the required offset from the label and the address of the current instruction. If the offset is too large, the assembler produces an error.

Note:

For most instructions, the value of the PC is the address of the current instruction plus 4 bytes.

The assembler might permit other syntaxes for PC-relative expressions, such as a label plus or minus a number, or an expression of the form [PC,#imm].

#### 3.3.6 Conditional execution

Most data processing instructions update the condition flags in the application program status register (APSR) according to the result of the operation, see Section 2.1.3 Core registers. Some instructions update all flags, and some only update a subset. If a flag is not updated, the original value is preserved. See the instruction descriptions for the flags that they affect.

The user can execute a conditional branch instruction, based on the condition flags set in another instruction, either:

- Immediately after the instruction that updated the flags.

- After any number of intervening instructions that have not updated the flags.

On the Cortex-M0+ processor, conditional execution is available by using conditional branches.

This section describes:

- The condition flags.

- Condition code suffixes.

#### The condition flags

The APSR contains the following condition flags:

- N Set to 1 when the result of the operation was negative, cleared to 0 otherwise